1. Understand the LPC1768’s Interrupt System

The ARM Cortex-M3 processor of the LPC1768 has a sophisticated Nested Vectored Interrupt Controller (NVIC). Strong interrupt management features offered by the NVIC include: Grouping of interrupt priorities Handling nested interrupts numerous interrupt sources from external interrupts, timers, UARTs, ADCs, and GPIOs, among other peripherals. The Cortex-M3

processor has 16 externally programmable interrupt priority levels and supports up to 240 interrupt sources.

2. Fundamental Ideas:

Interrupt Vector Table and NVIC Handling interrupt requests (IRQs) falls under the purview of the NVIC.

In the interrupt vector table, which links interrupt service routines (ISRs) to the corresponding interrupt sources, each IRQ is represented by a distinct vector. Interrupt Vector Table: Each interrupt’s corresponding ISR address is listed in this table. The processor searches the table for the interrupt handler (ISR) and begins running it when an interrupt occurs. Priority Levels: There is a priority level assigned to each interruption. Eight programmable priority levels are possible with the ARM Cortex-M3 (assuming four bits are used for priority). Higher priority levels are represented by lower numerical values.

3. Disrupt the Management of Priorities

You can adjust each interrupt source’s priority using the LPC1768’s NVIC, which establishes:

The interrupt’s pre-emption priority controls its capacity to pre-empt (interrupt) another interrupt that is presently running. Lower priority interrupts may be interrupted by higher preemption priority interrupts.

When there are several interrupts with the same preemption priority, subpriority is used to control how they are handled. The order in which they are serviced depends on their subpriority.

- Setting Up Priorities for Interrupts

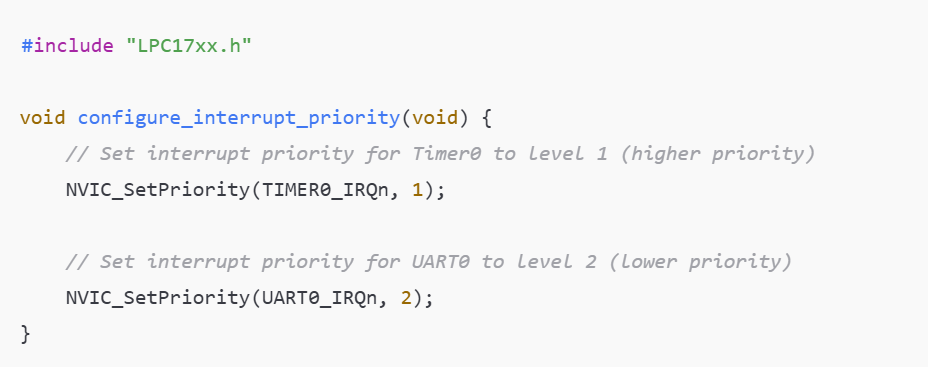

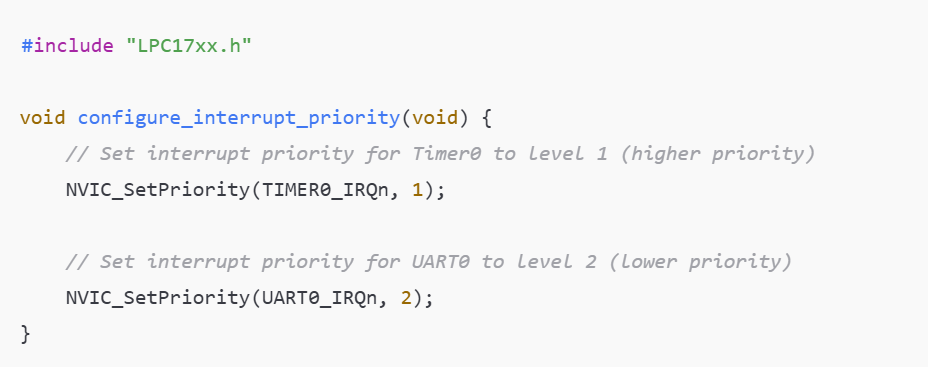

The NVIC_SetPriority function in the LPC1768’s software libraries allows you to set interrupt priorities. The highest priority is zero, and the lowest priority is 255. For instance:

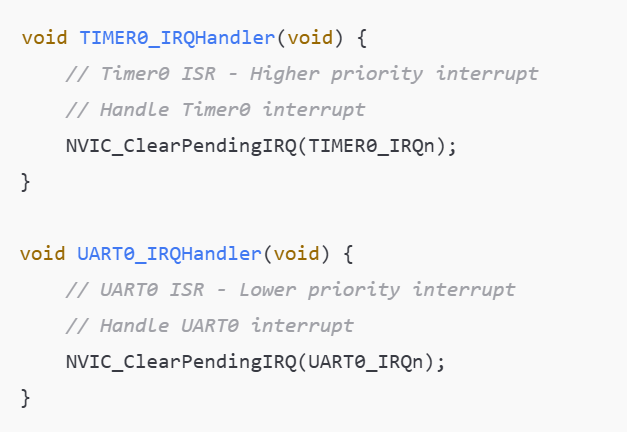

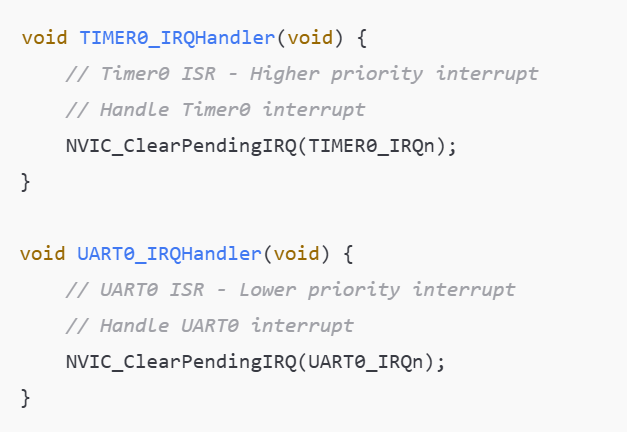

4. Nestled Interrupts

An interrupt can be interrupted by a higher-priority interrupt thanks to the Cortex-M3’snestedinterrupt feature. This implies that a new interrupt with a higher priority can preempt an interrupt service routine (ISR) that is currently running and begin running. The lower-priority ISR starts up again after the higher-priority ISR is finished.

- Making Nested Interrupts Possible

You must make sure that the global interrupt enable bit is set and that the NVIC is appropriately configured for priority levels in order to enable nested interrupts on the LPC1768. Once these parameters are set, nesting is automatically supported by the ARM Cortex-M3.

An illustration of turning on global interrupts:

- Example of Interrupt Prioritization

Now let’s look at an example where Timer0 is more important than UART0. The system will begin running the Timer0 ISR as soon as Timer0 generates an interrupt. The Timer0 ISR will be preempted if a UART0 interrupt with a higher priority occurs while the Timer0 ISR is running.

Priorities and Nested Interrupts in the LPC1768’s Advanced Interrupt Handling Based on the ARM Cortex-M3 core, the LPC1768 microcontroller has an advanced interrupt system that enables effective real-time processing in embedded systems.

For applications that need accurate and quick responses to numerous events, this paper examines advanced interrupt handling strategies on the LPC1768 with an emphasis on interrupt priorities and nested interrupts.

In this example, if the UART0 interrupt occurs while the Timer0 ISR is running, and UART0 has a higher priority (lower priority number), the Timer0 ISR will be interrupted and the UART0 ISR will run first.

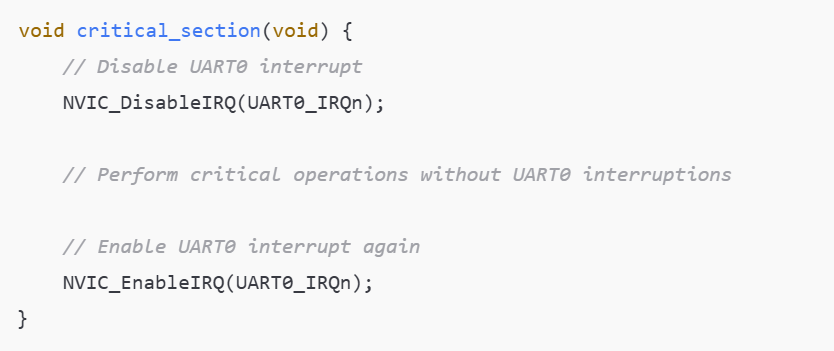

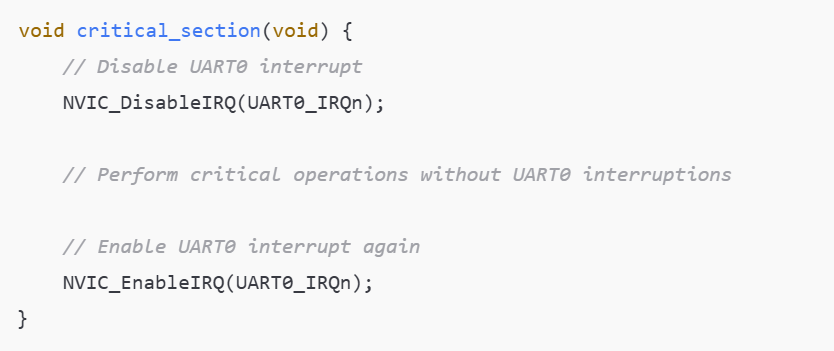

5. Masking Interrupts

Masking interrupts allows you to disable specific interrupts while continuing to service other interrupts. This is useful for critical sections of your application where you want to temporarily prevent interrupts.

You can mask and unmask interrupts using the NVIC_DisableIRQ and NVIC_EnableIRQ functions.

6. Interrupt Latency and Efficiency

Interrupt latency is the time it takes for the processor to respond to an interrupt request after it occurs. There are two main factors that affect latency:

Interrupt priority: Higher priority interrupts have lower latency because they anticipate lower priority interrupts.

Global interrupt flag: If the global interrupt flag is disabled, the processor cannot service interrupts until it is re-enabled. To minimize interrupt latency in real-time systems, consider the following tips:

Use appropriate priority levels to ensure that high-priority interrupts are serviced promptly.

Avoid long or blocking code in ISRs.

Use an efficient interrupt handling strategy to avoid unnecessary delays.

7. Optimizing nested interrupts

Nested interrupts improve the responsiveness of embedded systems. However, improper nesting can cause problems, such as:

Stack overflow: If deep nesting is required for interrupt handling, ensure that the interrupt stack is large enough to avoid stack overflow.

Context switching overhead: It is important to balance interrupt frequency and system performance, as frequent interleaving can increase the overhead of switching between ISRs.

You can use a CMSIS RTOS (Real-time Operating System) or other real-time scheduling algorithm to optimize the handling of nested interrupts, effectively manage tasks, and minimize unnecessary interrupts.

8. Common interrupt handling errors

Interrupt priority inversion:

If not managed properly, lower priority interrupts can block higher priority interrupts. To avoid this, make sure your priority system is well thought out.

Long ISRs: ISRs should be as short as possible. If processing within the ISR takes too long, it can cause system delays. Shared resources: Interrupts that modify shared resources must be synchronized to avoid race conditions.

Conclusion

Effective interrupt handling is critical to the performance of your LPC1768 embedded system. Understanding interrupt priorities, interleaving, and proper configuration of the NVIC will help you develop responsive and efficient applications. Proper management of interrupt priorities and interleaving can significantly improve the real-time performance of your embedded system. Always ensure that your ISRs are optimized to minimize execution time and avoid long processing times that can delay critical tasks.