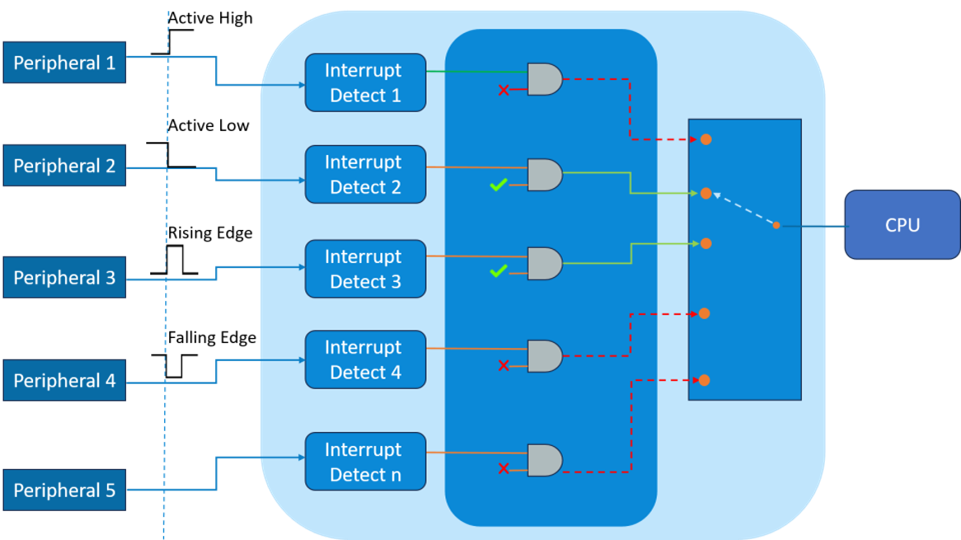

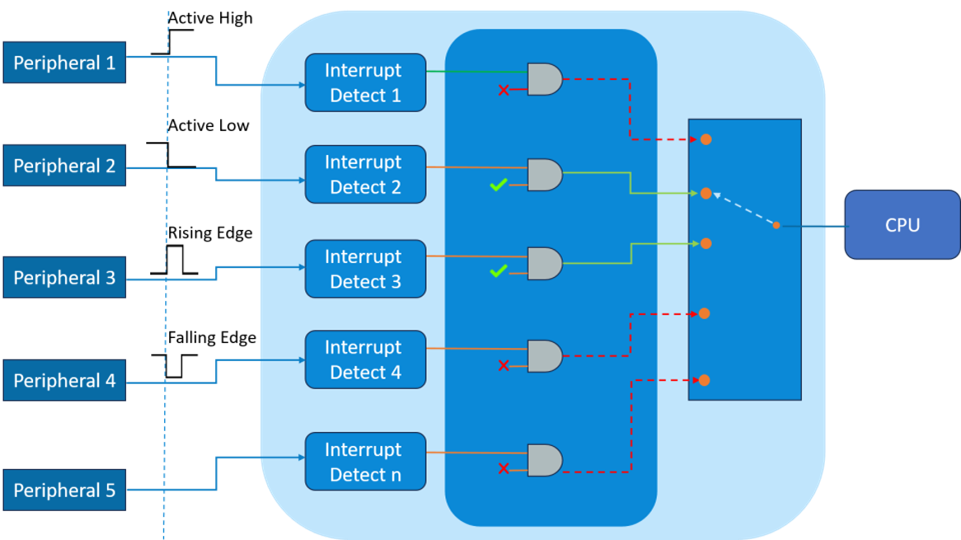

A programmable peripheral known as an interrupt controller is responsible for handling interrupt requests from hardware and other peripherals to the CPU. The evolution of processor standards has led to the development of an Interrupt Controller, which alleviates the workload on CPU designs. The interrupt controller serves as a programmable component that controls the activation and deactivation of interrupt requests, as well as the prioritization of these requests. Due to the limited number of hardware lines and computational power, the CPU faces certain restrictions, By multiplexing interrupts from different peripherals, the interrupt controller broadens the CPU’s ability to manage multiple interrupt requests.

Upon the activation of an interrupt, the CPU is alerted with the specific interrupt number. The specific interrupt number employed to trigger the relevant interrupt service routine (ISR) within the CPU.

The ARM Architecture is designed to handle multiple types of interrupt requests

- IRQs: Multiple sources can be supported concurrently by the Interrupt ReQuest type. This is particularly appropriate for applications that operate outside of real-time constraints, Please be aware that a slight delay in response could happen because we are utilizing multiple sources to address the interruption. Interrupt Request Lines employed in standard applications.

- FIQs: Only one source of interrupt can be supported at a time by the Fast Interrupt Request type. With dedicated register bank support for interrupts, FIQ minimizes lead time by avoiding the need for stacking and unstacking in standard program execution.